モジュール詳細

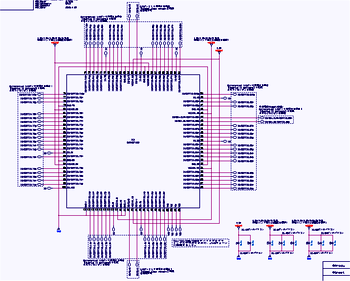

FPGA/CPLD

5M240ZT100

FPGA/CPLD

メーカー

主要部品型名

モジュール仕様・特長

■ 低コストと低消費電力で不揮発性アーキテクチャを提供

■ インスタント・オン(0.5 ミリ秒以下)のコンフィギュレーション時間

■ わずか 25 uA の低い待機時電流、迅速なパワーダウン/ リセット動作

■ 高速伝播遅延およびClock-to-Output タイム

■ 内蔵オシレータ

■ 200 Mbps までのデータ・レートに対応しているエミュレートされたRSDS 出力をサポート

■ 304 Mbps までのデータ・レートに対応しているエミュレートされたLVDS 出力をサポート

■ ロジック・アレイ・ブロック(LAB)ごとに2 つのクロックを使用できる4 つのグローバル・クロック

■ 最大8 ビットの不揮発性情報を格納するユーザー・フラッシュ・メモリ(UFM)ブロック( 最大1000 リード/ ライト・サイクルまで)

■ デバイス・コアに電源を供給する単一の1.8V 電源

■ 3.3 V、2.5 V、1.8 V、1.5 V および1.2 V のロジック・レベルをサポートするMultiVolt I/O インタフェース

■ プログラマブル・スルー・レート、ドライブ強度、バス・ホールド、およびプログラマブル・プルアップ抵抗など、バスを扱いやすいアーキテクチャ

■ 耐ノイズ製に優れた入力を可能にするシュミット・トリガ(ピンごとにプログラム可能)

■ I/O が3.3V のPCI-SIGR PCI Local Bus Specification(Rev. 2.2)に完全準拠

■ ホット・ソケット仕様に準拠

■ IEEE Std. 1149.1-1990 準拠のJTAG(Joint Test Action Group)バウンダリ・スキャン・テスト(BST)回路を内蔵

■ インスタント・オン(0.5 ミリ秒以下)のコンフィギュレーション時間

■ わずか 25 uA の低い待機時電流、迅速なパワーダウン/ リセット動作

■ 高速伝播遅延およびClock-to-Output タイム

■ 内蔵オシレータ

■ 200 Mbps までのデータ・レートに対応しているエミュレートされたRSDS 出力をサポート

■ 304 Mbps までのデータ・レートに対応しているエミュレートされたLVDS 出力をサポート

■ ロジック・アレイ・ブロック(LAB)ごとに2 つのクロックを使用できる4 つのグローバル・クロック

■ 最大8 ビットの不揮発性情報を格納するユーザー・フラッシュ・メモリ(UFM)ブロック( 最大1000 リード/ ライト・サイクルまで)

■ デバイス・コアに電源を供給する単一の1.8V 電源

■ 3.3 V、2.5 V、1.8 V、1.5 V および1.2 V のロジック・レベルをサポートするMultiVolt I/O インタフェース

■ プログラマブル・スルー・レート、ドライブ強度、バス・ホールド、およびプログラマブル・プルアップ抵抗など、バスを扱いやすいアーキテクチャ

■ 耐ノイズ製に優れた入力を可能にするシュミット・トリガ(ピンごとにプログラム可能)

■ I/O が3.3V のPCI-SIGR PCI Local Bus Specification(Rev. 2.2)に完全準拠

■ ホット・ソケット仕様に準拠

■ IEEE Std. 1149.1-1990 準拠のJTAG(Joint Test Action Group)バウンダリ・スキャン・テスト(BST)回路を内蔵

備考

正式型番は詳細機能(温度グレード/スピードグレード/RoHS対応条件など)によって決定します。

詳細についてはメーカーにお問い合わせ下さい。

詳細についてはメーカーにお問い合わせ下さい。